Verilog는 다양한 연산자를 가지고 있어, 임이의 회로에 대하여 다양한 기술을 가능하게 한다.

비트 연산자(Bitwise Operators)

비트 연산자는 비트 레벨의 논리 연산을 표현한다.

| 비트 연산자 | 동작 |

| ~ | "bitwise"NOT |

| & / ~& | "bitwise"AND,NAND |

| | / ~| | "bitwise"OR/NOR |

| ^ / ~^ | "bitwise"XOR/XNOR |

비트와이즈 연산자의 사용 예는 다음과 같다. 출력은 4비트의 wire이다.

논리 연산자(Logical Operators)

논리 연산자느 연산 결과가 참 또는 거짓 중 하나가 된다.

| 논리 연산자 | 동작 |

| && | "logical"AND |

| || | "logical"OR |

| ! | negation |

논리 연산자는 0이 아닌 수를 1로 취급한다. 다음 코드에서 a&b 연산의 경우 bitwise로 연산하여 결과가 4'b0000이 되겠지만 논리 연산의 경우 결과가 1'b1이 된다. 논리 연산의 결과는 1비트이다.

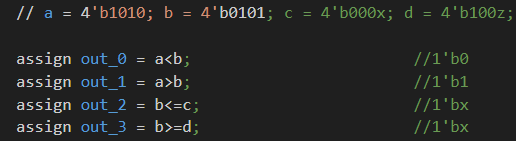

관계 연산자(Relation Operators)

관계 연산자'<', '>', '<=', '>='은 피연산자를 비교하기 위하여 사요한다. unknown 'x'나 high-impedence 'z'를비교할 경우 'x'를 출력한다.

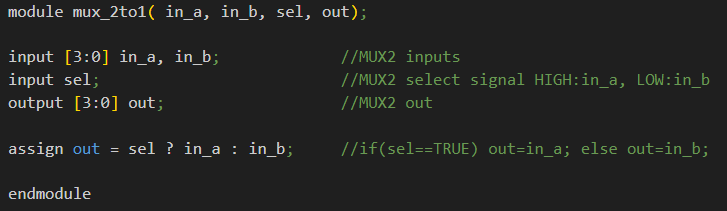

조건 연산자(Ternary Operator)

조건 연산자는 '? 첫 번째 항: 두 번째 항'을 사용하며, 그 값이 true이면 첫 번째 항을. false이면 두 번째 항을 결과로 한다. 조건 연산자를 사용하여 4비트 2입력 멀티플렉서를 기술하면 다음과 같다.

결합 연산자(Concatenation / Replication Operators)

결합 연산자는 스칼라 또는 벡터를 그룹으로 나타낼 때 유용하다. '{ }'는 비트를 연결(Concatenation)할 때 사용하며,

'{{ }}'는 비트를 복제(Replication)할 때 사용한다.

Replication 연산자는 그룹의 비트를 복제하기 위하여 사용된다. 예를 들면 1비트의 값을 3번 복제하여 3개의 비트의 값을 다음과 같이 표현할 수 있다. 신호 b가 세 번 복제되어 out_2의 12비트가 결정된다.

Concatenation 연산자는 여러 그룹의 비트를 연결한다. 예를 들면 출력 out_4는 a[1:0]과 c[1:0]을 연결하여 나타내며, 회로 설계 시 유용하게 사용된다.

시프트 연산자(Shift Operators)

시프트 연산자는 시프트 연산이 필요하거나 2의 승수를 곱하거나 나눌 때 사용한다. 논리(logical) 시프트 연산은 zero extension에 의해 새로운 비트들이 '0'으로 채워진다. '>>'과 '<<'는 각각 logical right와 logical left shift 연산이다.

산술(arithmetic) 시프트 연산은 오른쪽으로 쉬프트 하는 경우 부호 비트인 MSB값을 복제하는 sign-extension을 수행한다.

'>>>'과 '<<<'는 각각 arithmetic right와 left 시프트 연산이다. arithmetic shift는 signed로 선언된 변수에 한에서 적용된다. 만약 다음 코드의 변수 'a'가 signed로 선언되어 있지 않다면, 출력 out_0는 logical shift 연산 결과와 같이 4'b0001이 된다. 출력 신호가 모두 4비트라면 주석의 하위 4비트만이 연산 결과가 된다.

산술 연산자(Arithmetic Operators)

산술 연산자는 우리가 익숙하게 사용하는 '+, -, *, /, %, _'연산을 기술한다.

연산자의 우선순위(Operator Precedence)

지금까지 알아본 연산자의 우선순위는 다음과 같다. 우선순위를 암기하는 것보다 괄호를 적절하게 사용하는 것이 좋다.

| ~ | Not 높음 |

| *, /, % | multi, div, mod |

| +. - | add, sub |

| <<, >> | logical shift |

| <<<, >>> | arithmetic shift |

| <, <=, >, >= | comparison |

| ==, != | equal, not equal |

| &, ~& | AND, NAND |

| ^, ~^ | XOR, XNOR |

| |, ~| | OP, XOR |

| ?: | ternary operator 낮음 |

'... > 비메모리반도체' 카테고리의 다른 글

| Verilog HDL(Level of Modeling) (0) | 2024.07.25 |

|---|---|

| Verilog HDL(Instantiation) (0) | 2024.07.25 |

| Verilog HDL(Introduction) (0) | 2024.07.24 |

| 캡스톤 참고 논문링크 (1) | 2024.07.06 |

| 리눅스 환경 만들기(Windows 11의 WSL기반 Xilinx Vivado 설치) (0) | 2024.01.03 |