모듈 연결(Instantiation)

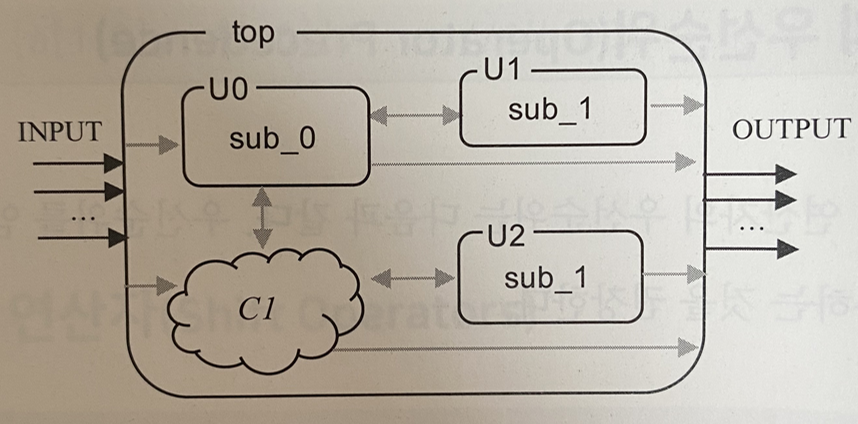

하드웨어는 보통 여러 개의 모듈로 이루어지며, 상위 계층과 하위 계층의 계층적 관계를 가지고 있다. 아래의 그림은 계층적 설계가 되어 있는 회로의 예이다. 최상위 계층의 모듈 top은 하위 sub_0 모듈을 U0라는 이름으로 포함하고 있으며, 하위 sub_1 모듈 두 개를 각각 U1과 U2라는 이름으로 포함하고 있다. 또한 내부 회로 C1이 있다.

이렇게 여러 개의 모듈을 포함하는 계층적 설계를 기술하기 위해서는 상위 모듈에서 하위 모듈을 인스턴스화 하고, 입출력 포트들을 신호로 연결하는 기술 방법이 필요하다.

상위 계층 모듈에서 하위 모듈을 인스턴스화 하고 연결하는 기술 방법은 두 가지가 있다.

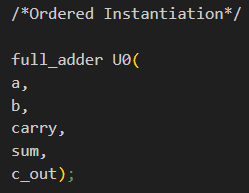

첫 번째는, 상위 모듈의 신호를 하위 모듈의 포트에 정의된 순서와 동일하게 기술하는 순서(ordered)에 의한 방법이다.

두 번째는 하위 모듈의 포트 명 앞에 ' . '을 넣고, 연결해 줄 상위 모듈의 신호를 괄호 안에 넣어 각각 독립적으로 연결하는 이름(named)에 따른 연결 방법이다.

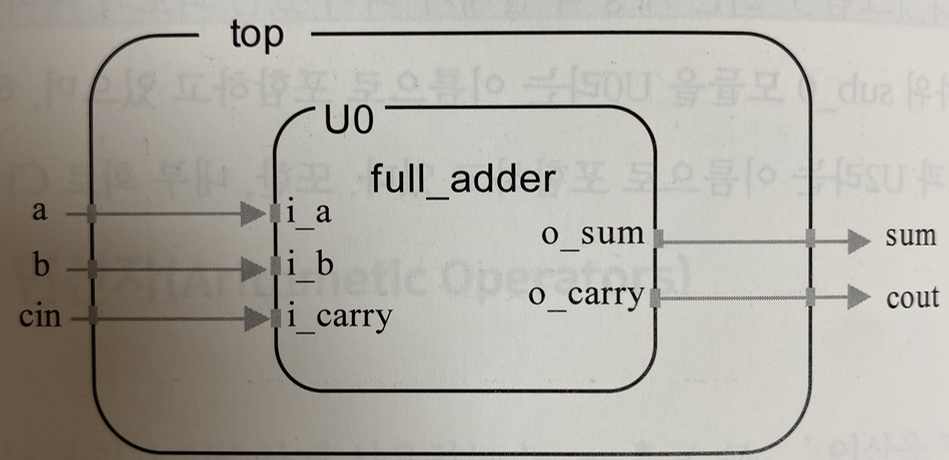

예를 들면 아래의 1비트 전가산기를 top 모듈에서 인스턴스화 하는 방법은 다음 두 가지가 있다.

Named instantiation을 사용하면 원래 하위 모듈의 포트 선언부를 그대로 복사해 와서 인스턴스화 할 수 있다.

이때 하위 모듈 원래의 포트 이름과 각 포트를 설명해주는 주석이 상위 모듈에서 그대로 유지되어 회로의 이해를 쉽게 하며 연결할 때의 실수를 줄일 수 있다.

내부 모듈 간의 연결을 위해서는, 모듈 간의 연결 신호가 미리 정의되어 있어야 한다. 즉 연결하고자 하는 신호를 wire로 선언하고, 각 모듈의 입출력 포트에 같은 이름의 wire를 연결해 주면 된다. 아래 그림은 내부 모듈 2개를 포함하는 상위 모듈의 예이다. 두 하위 모듈을 연결하는 신호 w_sig1과 w_sig2를 이용하여 두 모듈을 연결한다.

Named 인스턴스를 이용하여 기술하는 것이 좋다.

모듈 간의 신호 연결 시, 연결하는 신호의 폭은 동일해야 한다. 포트와 신호의 버스 폭이 다를 경우 0으로 채워지거나 작은 크기에 맞춰진다. 다시 말하면, 시뮬레이션을 할 때 오류(error)가 나지 않는다는 맣이다. 3비트 신호(w_sig1)가 4비트 입력(i_a)로 인가될 때, i_a[3]은 항상 0이 입력이 된다. 반대로 4비트 신호(w_sig2)가 3비트 입력(i_c)로 입력될 때, w_sig2[3]의 값은 무시된다.

버스 폭을 맞추지 않아서 임의로 0이 채워진 신호가 연결되거나, 하위 비트 신호만 연결된 회로를 디버깅하면서 많은 시간을 허비할 수도 있다. 모듈을 연결할 때는 Named Instantiation을 사용하고, 신호들의 버스 폭을 항상 생각하면서 설계해야한다.

사용하지 않는 포트는 이론적으로 연결하지 않을 수 있다. 그러나 입력 포트를 연결하지 않은 상태로 두는 것은 별로 좋은 방법은 아니다.

'... > 비메모리반도체' 카테고리의 다른 글

| Verilog HDL을 활용한 뉴런의 설계 (1) | 2024.08.21 |

|---|---|

| Verilog HDL(Level of Modeling) (0) | 2024.07.25 |

| Verilog HDL(Operators) (0) | 2024.07.25 |

| Verilog HDL(Introduction) (0) | 2024.07.24 |

| 캡스톤 참고 논문링크 (1) | 2024.07.06 |