이전의 포스팅에서도 말했지만 XOR problem이 있다.

- 가장 중요한 내용은 학습 알고리즘을 통한 bias와 weights의 조절이며, back

propagation learning이 일반적으로 사용됨. - 기대값과 실제 출력값과의 차이를 통해 weights를 보정하는 방법임.

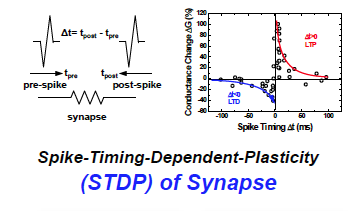

- Unsupervised learning 방법에 STDP가 있으며, 이는 입력과 동일한 출력을 얻

거나 pattern 인식 분야에 효과적임. - Learning 알고리즘 구현은 추후에 검토. (실제 응용에서는 학습은 CPU-GPU가

수행하고, FPGA는 inference로 사용되는 것이 일반적임.) - 대신 아래의 동작을 수행하는 뉴런을 설계하고자 함 (XOR의 경우 여러 가지

해법이 가능함).

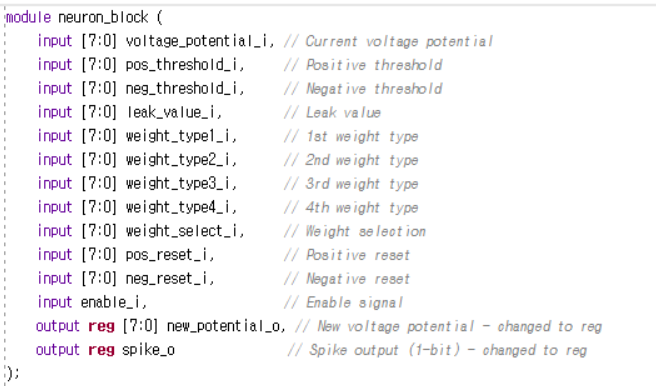

뉴런 동작 조건

- Multiplier 기능이 필요.

- Adder 기능이 필요.

- Sigmoid 기능이 필요. (Activation function)

- STDP 등의 구현과 저전력 동작을 위해서는 spiking에 따른 frequency가 정보를 담고 있어야 함.

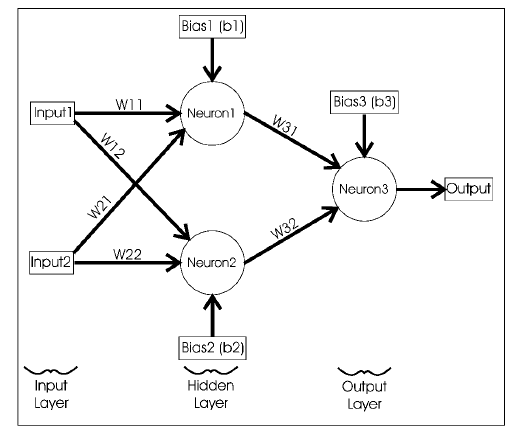

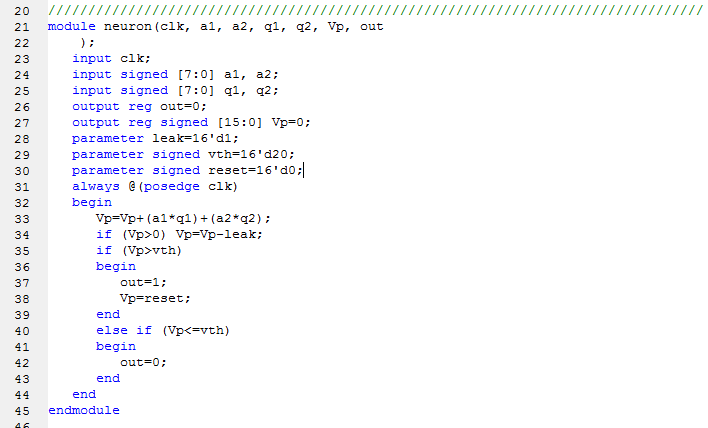

- 2 input neuron의 기본적인 형태 (sigmoid 함수 대신 step 함수 사용)

- 2 input neuron의 기본적인 형태 (sigmoid 함수 대신 step 함수 사용)

- 입력이 signed 8-bit이며 일정 시간이 지남에 따라 output이 pulse 형태로 출력

됨을 알 수 있음. Leaky integrate-and-fire의 기본 형태임.

- Multiplier와 Adder의 성능이 중요하며, 많은 부분을 차지하게 됨. (실제 FPGA에서 구현되는 경우 DSP로 변환되거나 LUT로 변환됨.)

XOR 동작을 위한 뉴런

- 입력은 1-bit이며, weights와 bias는 signed digit이어야 함.

- 단순 입력이 출력에 반영되는 combinational logic 형태임.

- 입력은 1-bit이며, weights와 bias는 signed digit이어야 함.

- MUX 형태로 곱셈을 구현하므로, 회로 영역이 작아짐.

XOR 동작을 위한 뉴럴 네트워크

- 은닉층을 포함하여 3개의 뉴런으로 구성됨.

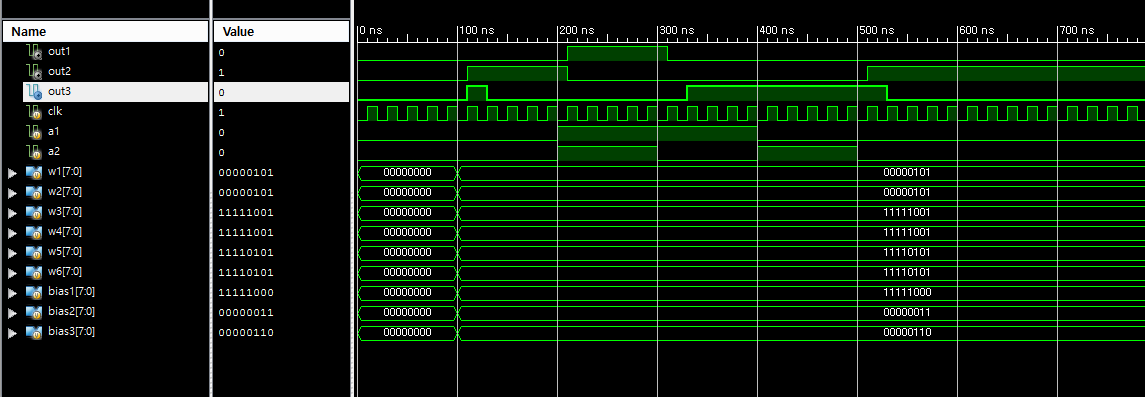

- Input stimulus는 아래와 같음.

- 동작 결과는 아래와 같음.

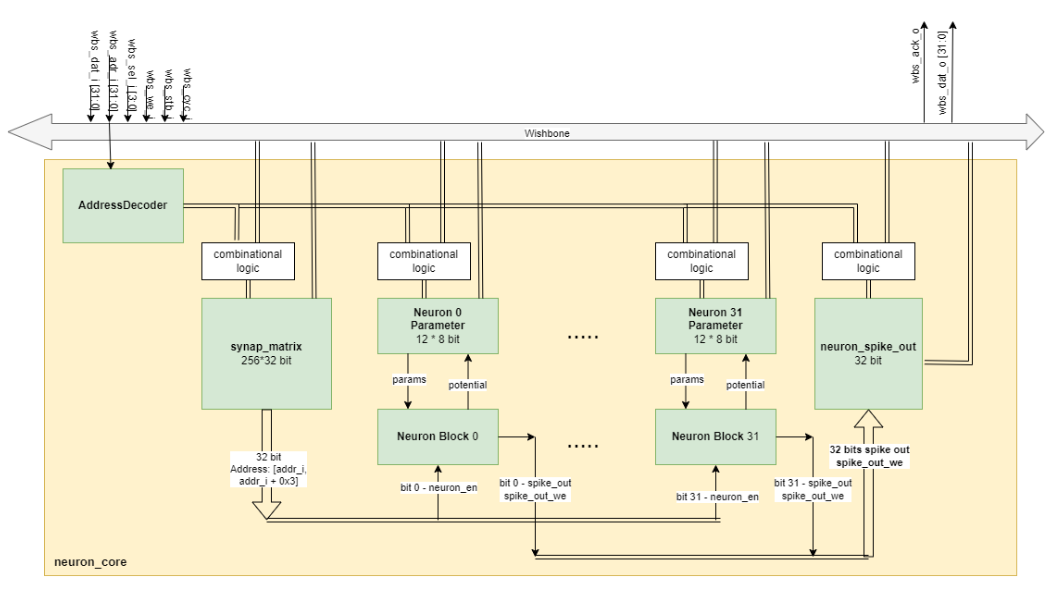

- A project dedicated to developing a hardware Integrated Circuit (IC) for a Spike Neural Network (SNN), powered by the RTL code generated by ChatGPT-4 with advanced optimizations.

- Energy Efficiency, Real-time Processing, Biomimetic Computation.

- RISC-V and SNNs

참고 링크: https://github.com/edabk-hust/edabk_brain_soc

- Membrane potential

- Vivado, HLS로 설계 -> IP 제작 -> Vitis (Hardwaresoftware co-simulation)

- Weights를 저장

- Weights를 저장하기 위한 용도로 사용되며, 뉴런의 수가 적은 경우에는 차지하

는 영역이 적지만, 뉴런의 수가 많아지면 급격히 증가하게 됨. - 대부분 memory를 사용하여 디지털 시냅스를 구성함.

- 간단한 사용은 register처럼 사용하는 것임.

- reg [39:0] mem1 [0:255]; //256 40-bit register

initial $readmemb(“file1”, mem1);

- reg [39:0] mem1 [0:255]; //256 40-bit register

- $readmemb(2진수 포맷), $readmemh(16진수 포맷)

- $readmemb(“파일명”, 메모리명, 시작주소, 마지막주소)

- Xilinx의 경우에는 다양한 block ram 등을 제공해 줌.

- 기본적인 사용은 RAMB16BWER (18 Kb)과 RAMB8BWER (9 Kb)의

primitive cell을 정의해서 사용함.

- Weights를 저장하기 위한 용도로 사용되며, 뉴런의 수가 적은 경우에는 차지하

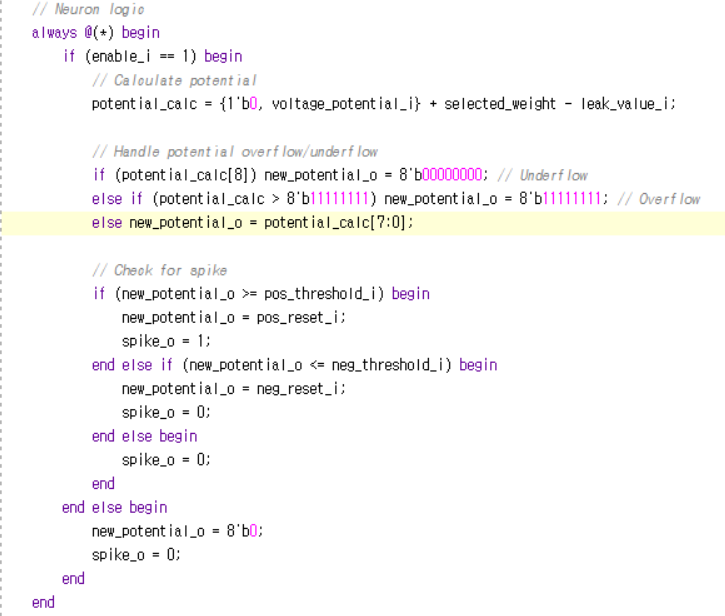

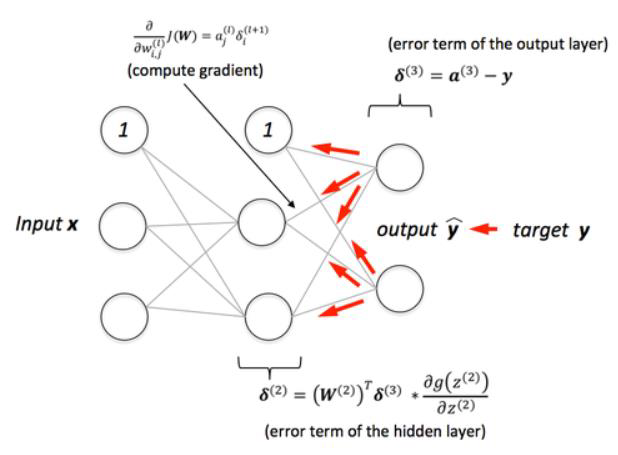

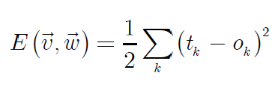

- Back propagation

- 뉴로모픽 시스템의 경우 학습이 중요하지만 계산량이 많아 대부분 외부에서 수행하는 경우가 많음. FPGA에서는 inference만 수행.

- 현재 가장 많이 사용되는 방식이 back propagation 방식임.

- 뉴로모픽 시스템에 학습을 구현하기 위해 간단한 형태로 구현하며, OR gate를

구현하는 것이 목표임. - 학습 알고리즘을 위해 실수를 사용 (1bit –sign, 15bit – 정수, 16bit – 소수).

- Adder, multiplier, sigmoid 함수 사용, error는 RMS로 정의.

- 위 식을 참고하여 간단한 연산만으로 back propagation 알고리즘의 구현이 가능함.

참고 링크: https://github.com/yashaelfaith/dnnbp

참고 링크: https://github.com/ChFrenkel/ODIN online-learning digital spiking neural network (SNN)

- STDP

- STDP 알고리즘의 경우 spike의 생성에 입력이 기인한 경우에는 연결을 강화하고, 그렇지 않은 경우에는 연결을 약화시키는 방법임.

- Unsupervised learning의 대표적인 경우이며, 패턴 인식 등에 효과적임.

728x90

'... > 비메모리반도체' 카테고리의 다른 글

| hls4ml (0) | 2024.08.22 |

|---|---|

| Vivado HLS 사용 (0) | 2024.08.22 |

| Verilog HDL(Level of Modeling) (0) | 2024.07.25 |

| Verilog HDL(Instantiation) (0) | 2024.07.25 |

| Verilog HDL(Operators) (0) | 2024.07.25 |