Vivado high-level synthesis

- C/C++로 작성된 system을 synthesis를 통해 Verilog 파일 등으로 변환 해줌.

- New project

- Add source code (header file 포함)

- Run C simulation

- Run C synthesis

- Run C/RTL co-simulation (solution에 있음).

- Export RTL (IP Catalog) implementation에 zip 파일 형태로 저장됨.

- 다른 프로젝트를 여는 경우에는 vivado command prompt에서 vivado_hls –f script.tcl 등을 실행해주면 프로젝가 생성되며, 해당 프로젝트를 vivado_hls –p project를 실행해 주면 됨.

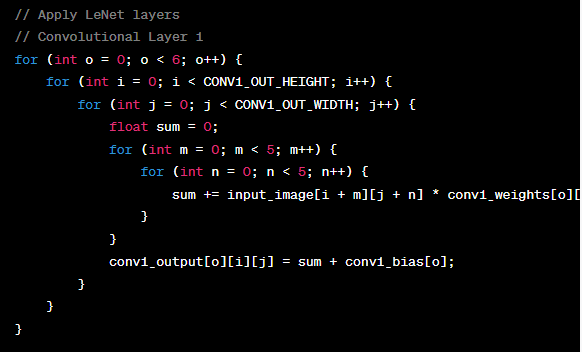

- 아래는 convolution neural network를 HLS를 사용하여 구현한 예임.

- Source에 해당 C/C++ 파일이 존재하여야 하며, top module이 정의되어 있음.

- Test bench에 main() 함수가 존재하여야 하며, top module을 import 함.

- Solution의 settings를 사용하면 원하는 part를 선택할 수 있음.

- 참고 링크: https://github.com/karthisugumar/CSE237C_FinalProject_ksugumar_iameerud

- 참고 링크: https://github.com/FloyedShen/mnist_hls

GitHub - FloyedShen/mnist_hls: Lenet for MNIST handwritten digit recognition using Vivado hls tool

Lenet for MNIST handwritten digit recognition using Vivado hls tool - FloyedShen/mnist_hls

github.com

- 각 module은 알고리즘을 C/C++로 옮겨 작성하면 됨.

- 아래는 conv2d_C1이 HLS에 의해 Verilog 형태로 변환된 것임. (baseline 사용)

Binary neural networks : https://github.com/ralbertazzi/bnn

- 파형을 확인하고 싶은 경우에는 C/RTL cosimulation에서 dump trace를 꼭 체크하여야 함. (port)

- Open wave viewer가 활성화됨.

- 현재의 Lenet의 경우에는 시간이 오래 걸려 파형 확인은 안 함.

- xc7z020clg400-1 (낮은 성능), -3 (높은 성능)

- Pynq (python productivity for Zynq)는 별도의 보드인 Pynq-1, -2가 존재하지만 Zynq로도 Pynq 이미지를 사용하여 동일하게 동작시킬 수 있음.(https://github.com/Xilinx/PYNQ)

- host name : pynq

- ID : xilinx

- PW : xilinx

- Bit 파일과 hwh 파일 저장

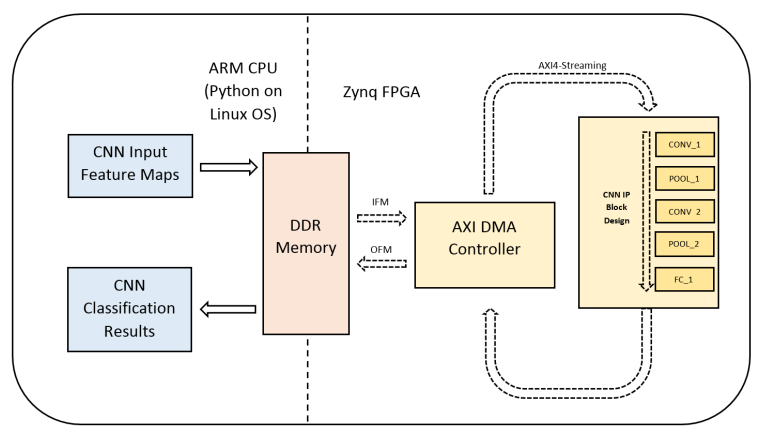

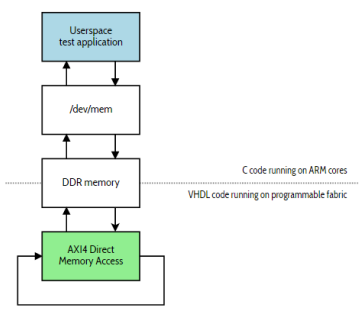

- Export RTL의 zip file을 vivado에서 IP로 불러서 Block design (bd)을 수행함 (PS와 AXI interface)

- Project settings에서 IP-Repository 선택한 후 추가.

- AXI4 interface 사용 (AXI4, AXI4-lite(address 포함), AXI-Stream – 고속이고 주소 지정이 없음.)

- 참고 링크: https://github.com/awai54st/PYNQ-Classification

GitHub - awai54st/PYNQ-Classification: Python on Zynq FPGA for Convolutional Neural Networks

Python on Zynq FPGA for Convolutional Neural Networks - awai54st/PYNQ-Classification

github.com

- Overlay 사용 (pynq) – 사용하고자 하는 bit file을 다운로드해서 사용함. (hwh도 필요함. 하드웨어 정의 파일)

- Vitis 등 사용.

전체 구성 (overlay IP 사용)

- Block design 파일 (ZYNQ - M_AXI_GP0 - PS master, PL slave, S_AXI_GP0 - PS slave, PL master)

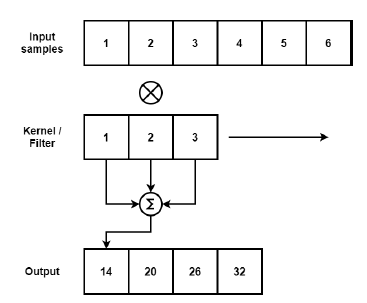

- 아래의 함수를 C/C++로 구현

- 1D convolution 예

이는 ChatGPT를 통해 쉽게 얻을 수 있음

728x90

'... > 비메모리반도체' 카테고리의 다른 글

| Verilog HDL을 사용한 디지털 로직 설계 (0) | 2024.08.22 |

|---|---|

| hls4ml (0) | 2024.08.22 |

| Verilog HDL을 활용한 뉴런의 설계 (1) | 2024.08.21 |

| Verilog HDL(Level of Modeling) (0) | 2024.07.25 |

| Verilog HDL(Instantiation) (0) | 2024.07.25 |