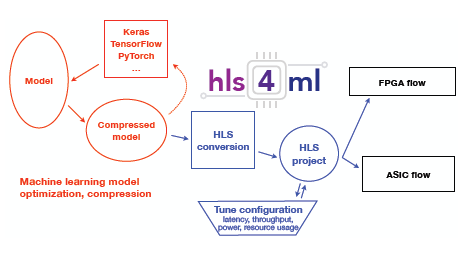

여러 종류의 SW -> Verilog HDL 플랫폼이 존재하며, 그 중 대표적인 예가 hls4ml임.

Keras, tensorflow 등을 Verilog HDL로 바꿔주지만 parameter 수가 적어야 함.

hls4ml의 내부 구조

참고 링크: https://github.com/fastmachinelearning/hls4ml

GitHub - fastmachinelearning/hls4ml: Machine learning on FPGAs using HLS

Machine learning on FPGAs using HLS. Contribute to fastmachinelearning/hls4ml development by creating an account on GitHub.

github.com

- hls4ml/hls4ml/templates/vivado/nnet_utils/

❑ // *************************************************

❑ // RELU Activation

❑ // template<class data_T, class res_T, typename CONFIG_T>

❑ void relu(data_T data[CONFIG_T::n_in], res_T res[CONFIG_T::n_in])

❑ {

❑ #pragma HLS PIPELINE

❑ data_T datareg;

❑ for (int ii=0; ii<CONFIG_T::n_in; ii++) {

❑ datareg = data[ii];

❑ if (datareg > 0) res[ii] = datareg;

❑ else res[ii] = 0;

❑ }

❑ }

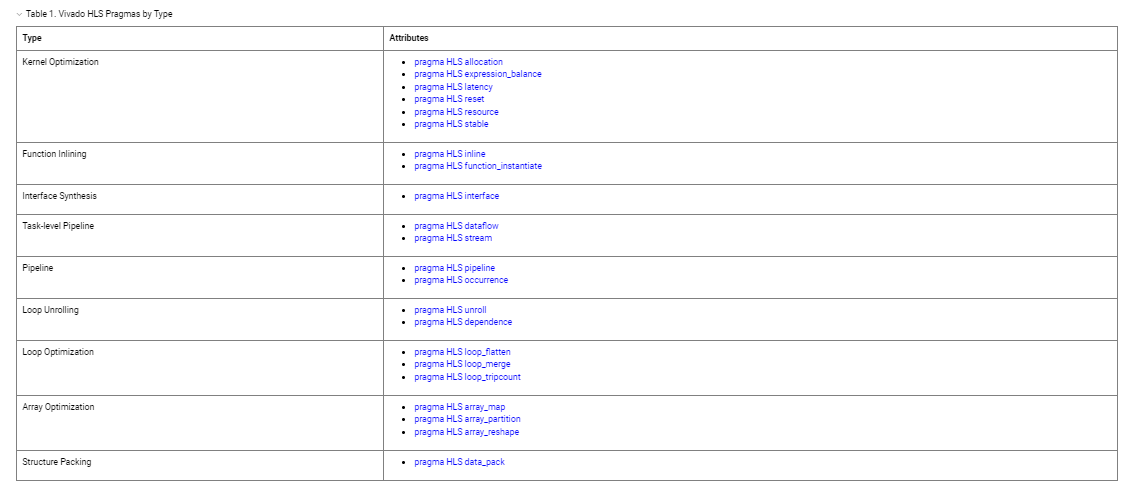

- HLS tool also provides pragmas that can be used to optimize the design: reduce latency, improve throughput performance, and reduce area and device resource usage of the resulting RTL code.

- Hls를 사용하여 각 블록을 불러와 project를 만든 후 synthesis를 통해 Verilog HDL 파일로 변환해 줌. (이는 myproject_prj의 synthesis에서 모든 .v 파일을 불러오면 됨.)

- Vivado Accelerator를 사용하면 pynq-z2에 해당되는 bit 파일 생성까지도 가능함.

이를 이용하여 앞으로 연구 방향

- SNN 구현 (저전력 회로, 학습 알고리즘 함께 구현)

- Digital logic을 직접 구현 (Neuron, synapse) – resource optimization

- 플랫폼 활용해서 적용하는 분야

Vivado HLS 사용

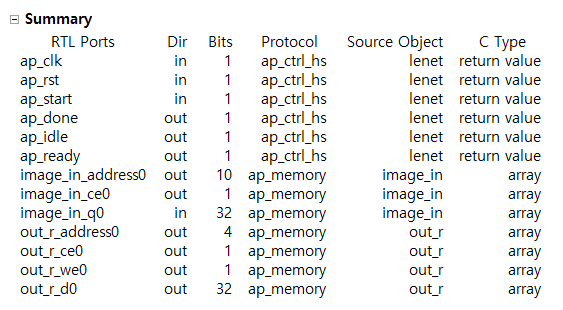

참고 : HLS interface

- s_axilite (AXI4-Lite) - awaddr, awprot, awvalid, awready (wirte address channel), wdata, wstrb, wvalid, wready (write data channel), bresp,bvalid, bready (write response channel), araddr, arprot, arvalid, arready(read access channel), rdata, rresp, rvalid, rready (read data channel)

- AXI4 - awaddr, awprot, awvalid, awready, awburst, awlen, awsize (wirte address channel), wdata, wstrb, wvalid, wready, wlast (write data channel), bresp, bvalid, bready (write response channel), araddr, arprot, arvalid, arready, arbust, arlen, arsize (read access channel), rdata, rresp, rvalid, rready, rlast (read data channel) (AXI4-lite는 32비트 고정)

- axis (AXI-Stream) - TVALID, TREADY, TDATA, (TLAST)

- ap_ctrl_none - 제어 신호 없음.

- ap_ctrl_hs (handshake) - ap_start, ap_done, ap_idle, ap_ready

- ap_ctrl_chain - ap_continue, ap_ready 신호 포함.

- bram interface - ADDR, DOUT, DIN, EN, WE

- #pragma HLS INTERFACE

- (axis port=in, axis port=out, ap_ctrl_none port=return, s_axilite port=return)

참고 : Pynq 연결

- Serial로 연결 – 장치 관리자에서 port를 확임함. (예: COM4) -> Putty 등을 사용하여 serial로 연결. (115200 baud)

- SSH로 열기도 가능함. (port : 22)

참고 : Ethernet 연결

- USB-Ethernet을 사용하는 경우 자동으로 Ethernet이 열림.

- 이 경우 Ethernet setting을 해 주어야 함.

- 보드의 ip가 192.168.2.99인 경우 PC는 192.168.2.x (0- 255이지만 99는 사용 중이라 안 됨.) - 중요함.

- 연결은 http://192.168.2.99를 실행하면 jupyter notebook이 열림.

- Upload를 사용하면 쉽게 파일 사용 가능함 (PC 파일을 이동.) 쉽게 PC로 다운로드도 가능함.

참고 : Overlay 결과

- Overlay를 사용하는 경우 아래의 결과를 얻을 수 있음.

728x90

'... > 비메모리반도체' 카테고리의 다른 글

| Verilog HDL을 사용한 디지털 로직 설계 (0) | 2024.08.22 |

|---|---|

| Vivado HLS 사용 (0) | 2024.08.22 |

| Verilog HDL을 활용한 뉴런의 설계 (1) | 2024.08.21 |

| Verilog HDL(Level of Modeling) (0) | 2024.07.25 |

| Verilog HDL(Instantiation) (0) | 2024.07.25 |