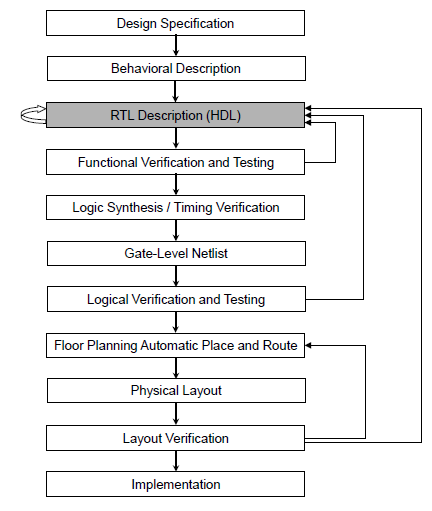

디지털 블록 설계 과정 (직접 설계)

- 프로그래밍 언어처럼 사용되며, 회로의 동작, 신호의 흐름을 기술함으로써 하드웨어의 설계가 이루어짐.

- 프로그래밍된 HDL을 논리합성을 통해 실제 IC로 구현이 가능해짐.

- 특정 ASIC 기술 및 공정에 무관하게 사용 가능.

- 다양한 레벨의 디자인 및 혼합 가능.

이때 FPGA는 IC칩 제작 전에 미리 검증하는 단계이고 합성을 통해 게이트 레벨에서 시뮬레이션을 하는 것은 IC 구현 과정의 일부분이라고 생각하면 된다.

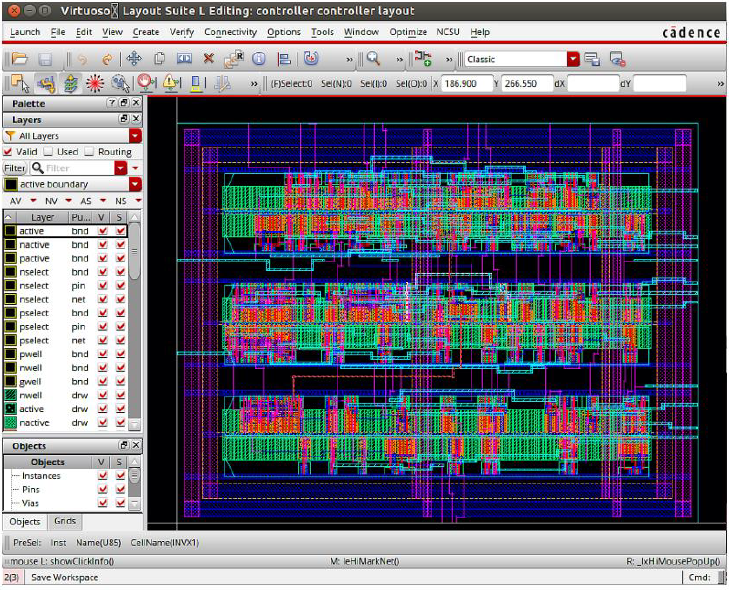

- Cadence Genus synthesis Solution (구 Encounter RTL Compiler)

- Innovus Implementation System (구 Encounter Digital Implementation)

- SoC Encounter

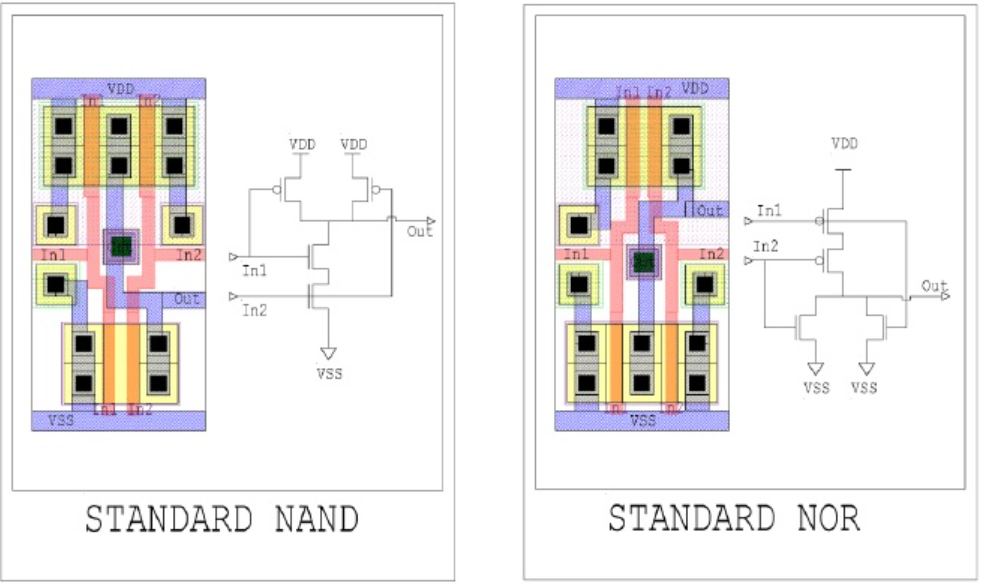

- Standard cell-based design으로 이루어지며, timing analysis가 중요함.

- Standard cell-based design – 셀들은 표준화된 높이를 가지게 되며, 이 외의 Power, Ground, Well 등이 자동 연결됨.

- 셀의 높이는 표준화되어 모두 같지만, 폭은 기능에 따라 변경할 수 있다.

- 이 셀들을 붙여서 배치하는 것만으로 Power, Ground, Well 등이 자동으로 연결된다.

- 설계의 시작은 Verilog HDL로 디지털 로직을 구현하고 검증하는 것임. (.v 파일)

- Innovus Implementation System (Auto place & route)

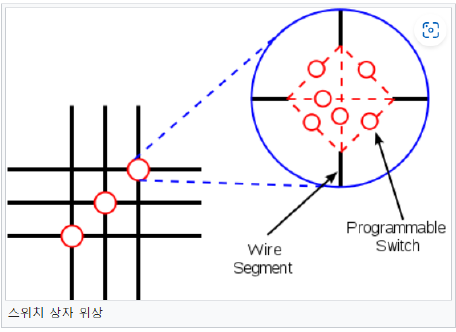

FPGA 개념

- FPGA는 조합논리회로를 위한 configurable logic blocks와 D Flip Flop, 여기에 연결을 위한 라우팅 채널로 구성되며 이는 프로그램으로 제어 가능.

디지털 로직을 쉽게 test할 수 있음.

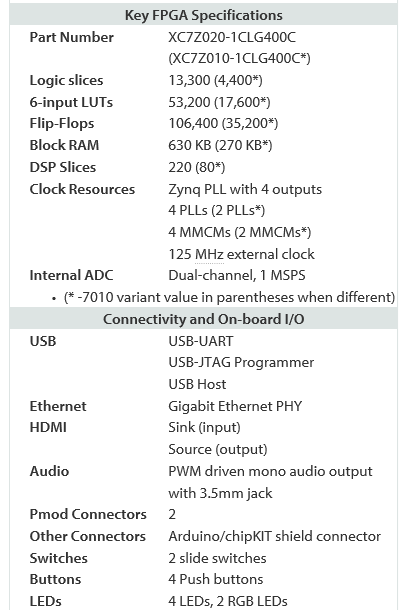

예 : Arty Z7-20 (다양한 입출력 제공)

- Arty Z7-20 실행을 위해 digilent’s board files와 xdc 파일이 필요함. (parts와 boards가 존재, boards는 input, output을 연결하기 편하도록 외부 회로와 연결한 형태임.)

- 참고 링크 : http://www.digilent.com

Digilent – Start Smart, Build Brilliant.

Shop now for USB test and measurement devices, FPGA development boards, programming solutions and educational products.

digilent.com

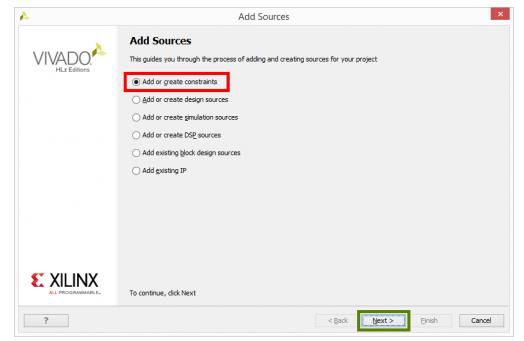

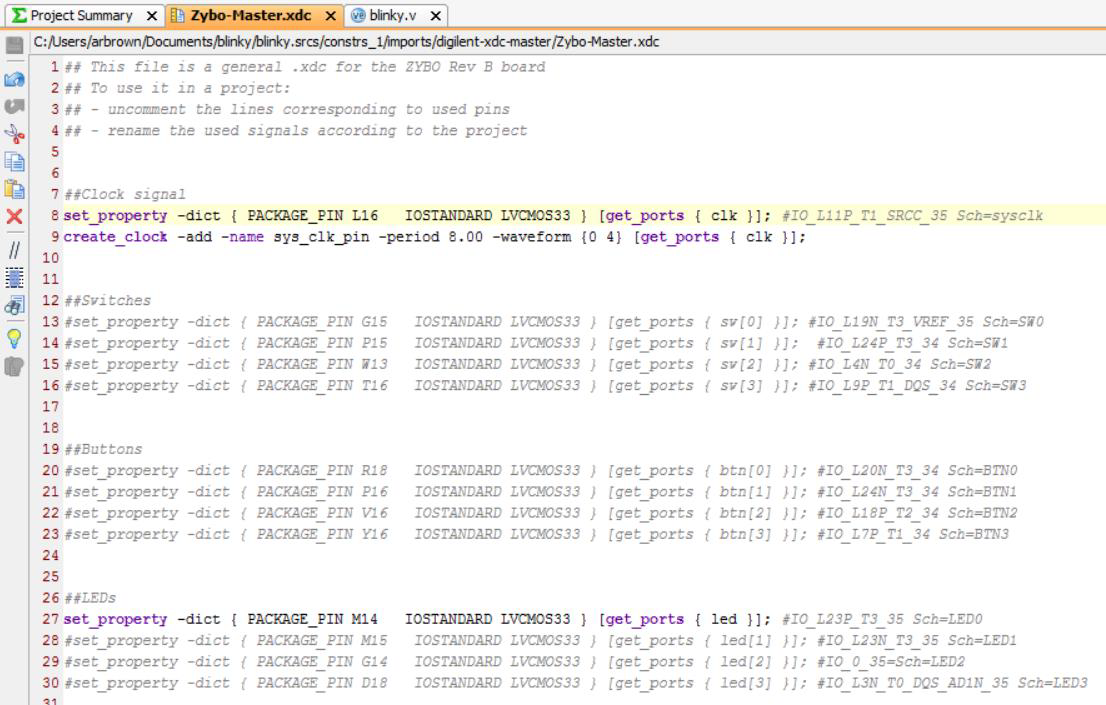

- Constraints는 pin mapping에 해당하며, 제조사에서 제공해 주는 xdc 파일임.

- 아래와 같이 Verilog code의 입력과 동일하게 지정해 주면 됨.

- Synthesis, implementation, and bitstream generation

- Hardware manager 창에서 part와 bitstream file을 선택해 준 후 program을 하면 원하는 파일이 FPGA에 다운로드 됨.

- 설계한 digital logic을 쉽게 test해 볼 수 있으며, 다양한 검증이 가능함.

- Xilinx -> AMD, Altera -> Intel

- 인공지능의 확장으로 C, Matlab, Python 등을 바로 변환해주는 software나 HLS (high-level synthesis)가 활용되고 있음. (디지털 로직의 장점은 병렬 연산이 가능하다는 것임.)

디지털 로직 기초

- 디지털 로직은 크게 조합논리회로와 순차논리회로로 구분됨.

- 각각은 synchronous, asynchronous 동작이 가능함.

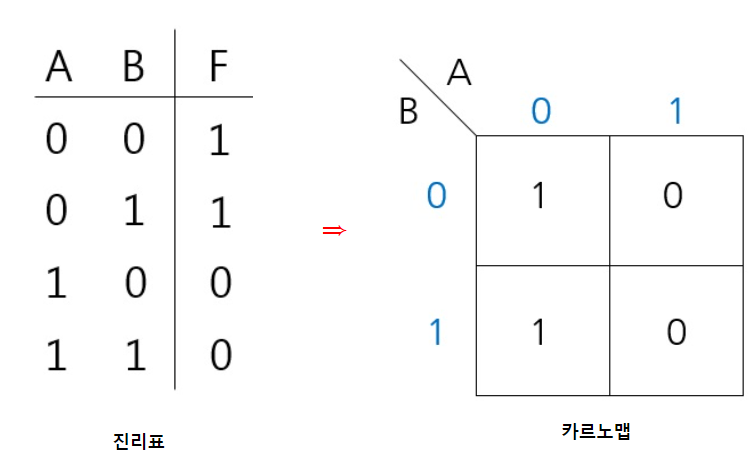

- 조합논리회로 - 함수로 쉽게 정리할 수 있음. (F=A’B’+A’B)

- 디지털 로직은 출력이 1 – high, 0 - low로 구분됨.

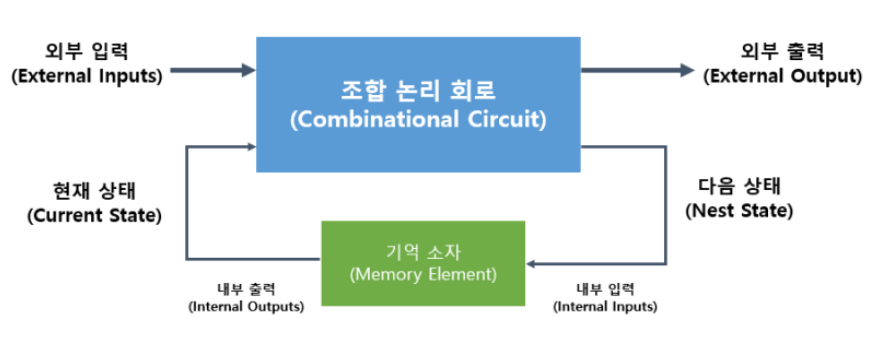

- 순차논리회로는 상태도를 활용하여 설계함.

- 상태도(FSM : Finite State Machine)

- 상태도는 순차논리회로의 동작을 표현 한 후에 Verilog 또는 VHDL로 설계

- FSM은 순차논리회로를 설계하는 하나의 방법임.

- Moore Machine(출력이 현재 상태에만 영향을 받음)과 Mealy machine(출력이 현재 상태와 입력의 영향을 받음)이 존재함. 주로 무어 머신을 사용함.

Verilog HDL(Hardware Description Language)

- Simulation을 수행할 수 있는 방법은 Cadence, Synopsys -> NCVerilog (Linux 기반), Icarus Verilog (text 기반), Verilator (text 기반, Linux 기반) 등이 있음.

- Xilinx사에서 제공하는 Vivado 설치 (GUI가 편함.)

- RTL(Register Transfer Language) 형태로 디지털 회로를 쉽게 설계할 수 있음 (High-Level 언어와 유사, 예:C/C++)

- -일반 프로그래밍 언어와 달리 하드웨어 중요한 특징인 시간과 동시성을 표현 할 수 있음

- 테스트 또는 검증을 시뮬레이션을 통해서 알 수 있음.

- 합성 tool에서 HDL을 컴파일 하여 gate-level 합성을 쉽게 구현 할 수 있음.

- 표준 HDL: Verilog & VHDL

- 아두이노, 라즈베리파이의 경우 instruction set을 기반으로 하지만 digital logic으로 연산하는 경우 병렬 연산 등이 가능한 장점을 가짐.

- 설계 생산성

- 자동 합성

- 시뮬레이터를 통한 테스트와 디버깅이 가능

- 회로도를 그리는 대신에 RTL로 디지털 회로를 설계

- 개발 기간 단축 (gate-level design)

- C 언어와 유사점

- 문법은 거의 유사

- 절차형(procedural) 및 순차형(sequential) 실행은 동일

- if ~ else문, case문, for loop문 등 사용

- 연산자: 논리(&,|,^..), 산술(+,-,*,/,%), 비교(>,<,<=,==)

- HDL 언어의 특성

- 동시성(concurrent)

- 병렬화(parallel)

- 추상화(abstraction)

Verilog HDL 기초

앞서 포스팅한 게시물에 더 자세한 설명이 있음

- 사용자는 design sources와 simulation sources (testbench)를 생성한 후 simulation 검증이 가능함.

- Design sources는 digital logic을 의미하며, 아래의 형태를 가짐.

- Module로 구성됨 – 입출력 및 내부 설계자가 사용할 변수 지정

- module – 입출력 및 내부 설계자가 사용할 변수 지정

- output 포트의 경우 값이 hold되어야 할 때 추가 reg 선언

- 모든 포트는 default로 wire로 인식

- Identifier (식별어)

- 사용자가 정의한 공백을 가지지 않는 문자열(임의 지정) module_name, port, function, object 등 첫 번째는 문자 또는 언더스코어(_)로 시작,대소문자 구분

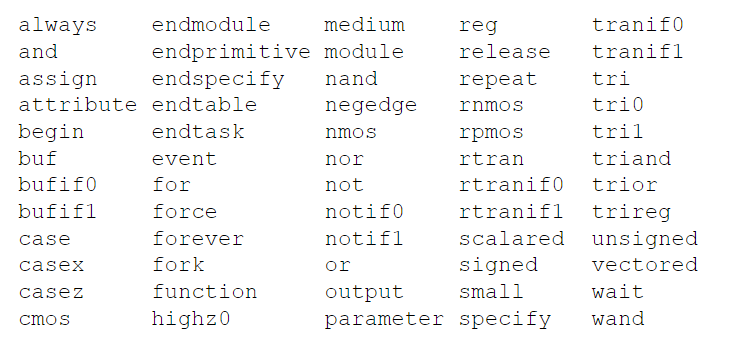

- Reserved word (예약어)

- Verilog HDL 구문을 위해 미리 정의된 문자열(임의 지정 불가) 사용자가 identifier로 사용할 수 없다 module, input, output, reg, endmodule, always 등

- Comment (주석)

- “//” 기호로 시작하는 문장

- 블록 주석문: /* ~ */ 로 표시

- 프로그램 수행에 영향을 미치지 않음

- Design을 위한 부연설명

Verilog data values

- 실제 디지털 회로에서 발생하는 값을 표현하기 위해서 Verilog는 4개의 data 값을 갖는다.

- 0: Logic zero, “low”

- Logic one, “high”

- z: High impedance(tri-state buses)

- X: unknown value(simulation) -시뮬레이터에서 wire에 초기값이 설정되지 않았거나 충돌이 일

어나는 것을 표현

데이터 형 (Data Type)

- wire (net 자료형)

- 논리적인 기능이나 행동 없이 단순한 선을 의미

- 물리적인 wire를 의미

- 게이트나 모듈간의 입력과 출력을 연결할 때 사용

- wire로 선언된 신호는 assign 문에서만 사용 가능하다.

- reg (variable 자료형)

- 순차회로에서 사용할 때에는 플립플롭이 된다.

- reg로 선언된 signal은 always 문에서만 사용 가능하다

- 테스트 벤치에서는 initial 문에서 사용한다.

- 새로운 이벤트가 발생하기 전까지 기존의 값을 유지한다.

Verilog 어휘 규칙

- 주석

- 라인주석: //

- 블럭주석: /* 주석 */

- 수 표현

- 정수형(integer)

- 10진수, 16진수, 8진수, 2진수로 표현 (d, h, o, b)

- integer i=100;

- 실수형(real)

- real a=12.232;

- Unsized 상수

- 32bit로 인식

- a=‘d10

- Sized 상수

- 4’b1001(=9, 4’d9, 4’h9, 4’o11)

- 정수형(integer)

- 상수의 부호

- -8’d6 = (8’b1111_1010=8’hFA)

- 밑줄 사용 수의 표현 (숫자의 차이는 없고, 구분을 용이하게 해 줌.)

- 27_195_000(27,195,000)

- 16’b0011_0101_0001_1111

- 32’h12ab_f0001

- begin ~ end

- initial, if, case, always 등을 사용할 때 블록을 지정할 때 사용

- C언어에서 {...}와 같은 개념

모듈 구성요소

- $ task, system tasks

- 구현 추상화 단계

- Behavioral model (행위 수준 모델링) – always

- 함수 블록간의 데이터 흐름을 표현

- 필요하다면 함수 블록간의 스케줄 삽입

- Dataflow model (데이터플로우 모델링) – assign

- 회로의 동작을 입력과 출력 간의 데이터 흐름으로 표현하는 방식. 이 방식에서 입력과 출력은 데이터의 흐름으로 표현되며, 이러한 데이터 흐름이 디지털 회로의 동작을 결정.

- Gate Level (Structural)

- Primitives or low-level components를 연결을 표현

- Switch model

- 추상화의 최하위 수준, 스위치와 기억 노드들로 모듈 구현

728x90

'... > 비메모리반도체' 카테고리의 다른 글

| hls4ml (0) | 2024.08.22 |

|---|---|

| Vivado HLS 사용 (0) | 2024.08.22 |

| Verilog HDL을 활용한 뉴런의 설계 (1) | 2024.08.21 |

| Verilog HDL(Level of Modeling) (0) | 2024.07.25 |

| Verilog HDL(Instantiation) (0) | 2024.07.25 |